# Bienvenue sur le cours de F6KGL

La séance de ce soir porte sur

### Technique Chapitre 8

### Amplificateurs opérationnels, circuits logiques

Ce document a servi pour le cours enregistré le 12/05/2023.

Ce document (*PDF*), le fichier audio (*MP3*) et les liens des vidéos (*YouTube*) sont disponibles sur la page <a href="https://f6kgl-f5kff.fr/lespodcasts/">https://f6kgl-f5kff.fr/lespodcasts/</a>

### 8-1) caractéristiques des amplificateurs opérationnels

Puce

- Présentation d'un amplificateur opérationnel

- circuits intégrés :

- étapes de fabrication

- détrompage, numérotation des pattes

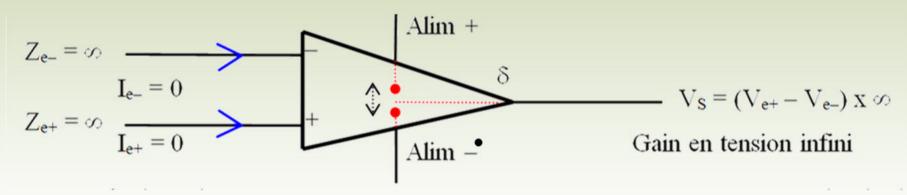

- L'amplificateur opérationnel possède

- deux entrées : une normale (+) et une inverseuse (-)

- une sortie différentielle  $(\delta)$ .

- Les amplificateurs opérationnels ont :

- une <u>impédance d'entrée infinie</u> (plus de 1  $M\Omega$ )

- un gain en tension (noté G) infini (gain = rapport, comme pour les transistors)

- une <u>impédance de sortie faible</u> (sortie connectée au + ou au -)

### 8-1) caractéristiques des amplificateurs opérationnels

### Caractéristiques (extrait de la datasheet - <a href="http://f6kgl.free.fr/741.pdf">http://f6kgl.free.fr/741.pdf</a>)

### μΑ741, μΑ741Υ GENERAL-PURPOSE OPERATIONAL AMPLIFIERS SLOS094B - NOVEMBER 1970 - REVISED SEPTEMBER 2000

- Short-Circuit Protection

- Offset-Voltage Null Capability

- Large Common-Mode and Differential Voltage Ranges

- No Frequency Compensation Required

- Low Power Consumption

- No Latch-Up

- Designed to Be Interchangeable With Fairchild µA741

### description

The µA741 is a general-purpose operational amplifier featuring offset-voltage null capability.

The high common-mode input voltage range and the absence of latch-up make the amplifier ideal for voltage-follower applications. The device is short-circuit protected and the internal frequency compensation ensures stability without external components. A low value potentiometer may be connected between the offset null inputs to null out the offset voltage as shown in Figure 2.

The µA741C is characterized for operation from 0°C to 70°C. The μA741I is characterized for operation from -40°C to 85°C. The µA741M is characterized for operation over the full military temperature range of -55°C to 125°C.

### μΑ741M . . . JG PACKAGE μΑ741C, μΑ741I . . . D, P, OR PW PACKAGE

### µA741M . . . U PACKAGE

µA741M . . . FK PACKAGE

NC - No internal connection

Copyright @ 2000, Texas instruments incorporate

### μΑ741, μΑ741Y GENERAL-PURPOSE OPERATIONAL AMPLIFIERS

SLOS094B - NOVEMBER 1970 - REVISED SEPTEMBER 2000

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

|                                                               | μA741C                       | μ <b>A741</b> Ι | μA741M     | UNIT |    |  |

|---------------------------------------------------------------|------------------------------|-----------------|------------|------|----|--|

| Supply voltage, V <sub>CC+</sub> (see Note 1)                 | 18                           | 22              | 22         | V    |    |  |

| Supply voltage, V <sub>CC</sub> _(see Note 1)                 | -18                          | -22             | -22        | V    |    |  |

| Differential input voltage, VID (see Note 2)                  | ±15                          | ±30             | ±30        | V    |    |  |

| Input voltage, V <sub>I</sub> any input (see Notes 1 and 3)   | ±15                          | ±15             | ±15        | V    |    |  |

| Voltage between offset null (either OFFSET N1 or OFFSET N2) a | ±15                          | ±0.5            | ±0.5       | V    |    |  |

| Duration of output short circuit (see Note 4)                 | unlimited                    | unlimited       | unlimited  |      |    |  |

| Continuous total power dissipation                            | See Dissipation Rating Table |                 |            |      |    |  |

| Operating free-air temperature range, TA                      | 0 to 70                      | -40 to 85       | -55 to 125 | °C   |    |  |

| Storage temperature range                                     | -65 to 150                   | -65 to 150      | -65 to 150 | °C   |    |  |

| Case temperature for 60 seconds                               | FK package                   |                 |            | 260  | °C |  |

| Lead temperature 1,6 mm (1/16 inch) from case for 60 seconds  | J, JG, or U package          |                 |            | 300  | °C |  |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds  | D, P, or PW package          | 260             | 260        |      | °C |  |

functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not

- implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values, unless otherwise noted, are with respect to the midpoint between V<sub>CC+</sub> and V<sub>CC+</sub>

- Differential voltages are at N+ with respect to IN-.

Differential voltages are at N+ with respect to IN-.

The magnitude of the input voltage must never exceed the magnitude of the supply voltage or 15 V, whichever is less.

The output may be shorted to good or either power supply. For the µAT-41M only, the unlimited duration of the short circuit applies

- at (or below) 125°C case temperature or 75°C free-air temperature.

### DISSIPATION RATING TARLE

| PACKAGE | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING<br>FACTOR | DERATE<br>ABOVE TA | TA = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING | T <sub>A</sub> = 125°C<br>POWER RATING |  |  |  |  |

|---------|---------------------------------------|--------------------|--------------------|---------------------------|---------------------------------------|----------------------------------------|--|--|--|--|

| D       | 500 mW                                | 5.8 mW/°C          | 64°C               | 484 mW                    | 377 mW                                | N/A                                    |  |  |  |  |

| FK      | 500 mW                                | 11.0 mW/°C         | 105°C              | 500 mW                    | 500 mW                                | 275 mW                                 |  |  |  |  |

| J       | 500 mW                                | 11.0 mW/°C         | 105°C              | 500 mW                    | 500 mW                                | 275 mW                                 |  |  |  |  |

| JG      | 500 mW                                | 8.4 mW/°C          | 90°C               | 500 mW                    | 500 mW                                | 210 mW                                 |  |  |  |  |

| P       | 500 mW                                | N/A                | N/A                | 500 mW                    | 500 mW                                | N/A                                    |  |  |  |  |

| PW      | 525 mW                                | 4.2 mW/°C          | 25°C               | 336 mW                    | N/A                                   | N/A                                    |  |  |  |  |

| U       | 500 mW                                | 5.4 mW/°C          | 57°C               | 432 mW                    | 351 mW                                | 135 mW                                 |  |  |  |  |

# 8-1) caractéristiques des amplificateurs opérationnels

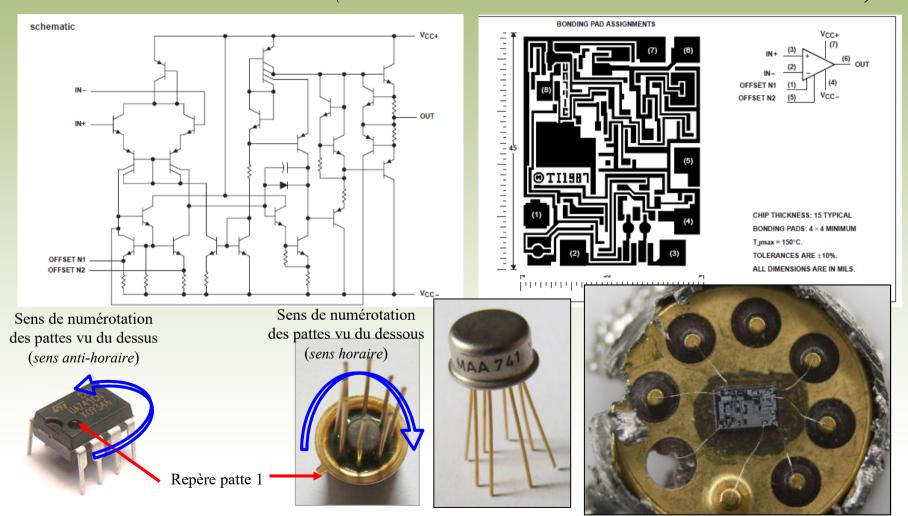

• Structure interne (extrait de la datasheet - <a href="http://f6kgl.free.fr/741.pdf">http://f6kgl.free.fr/741.pdf</a>)

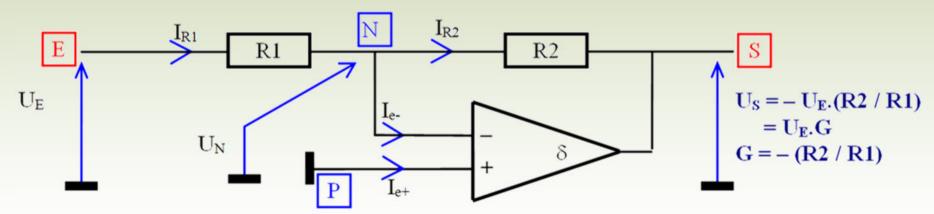

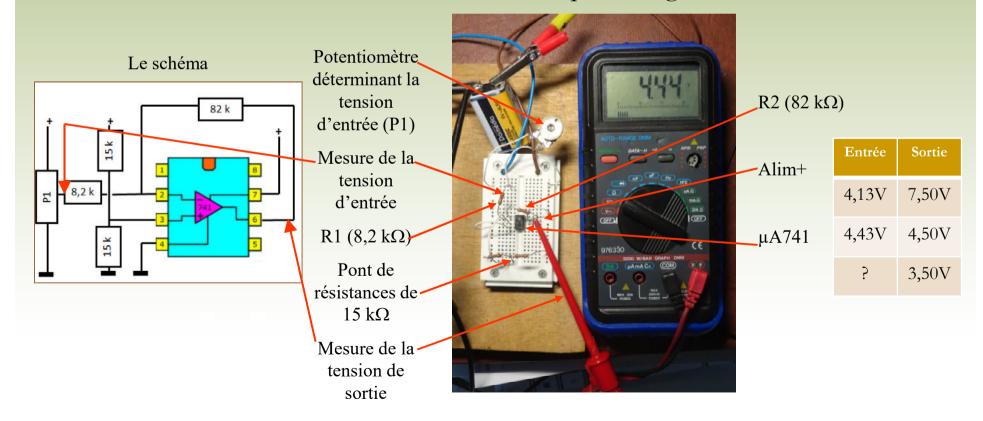

### 8-2) montage fondamental des amplificateurs opérationnels

- Le <u>montage fondamental</u> est un <u>amplificateur</u> inverseur de tension

- le signal d'entrée (E) est appliqué à l'entrée inverseuse via R1

- le montage fait appel à une contre-réaction grâce à R2

- le système cherche l'équilibre pour avoir  $U_N = U_P$

- le gain en tension à la sortie (S) est G = -(R2 / R1)

### 8-2) montage fondamental des amplificateurs opérationnels

• Exemple 1 : Quel est le gain de ce montage ?

gain =

$$-R2 / R1$$

=  $-25k / 5000 = -25000 / 5000$

=  $-5$

• Exemple 2 : Un amplificateur op monté en inverseur a un gain de –3 avec une résistance à l'entrée (R1) de 10 000 ohms. Quelle est la valeur de la résistance de contre-réaction (R2) ?

$$R2 = -(G \times R1) = -[(-3) \times 10\ 000] = 3 \times 10\ 000 = 30\ k\Omega$$

Exemple 3 : Quelle est la tension de sortie ?

gain =

$$-R2 / R1 = -500 / 100 = -5$$

Us = Ue x G =  $-0.5$  V x  $-5$  =  $2.5$  V

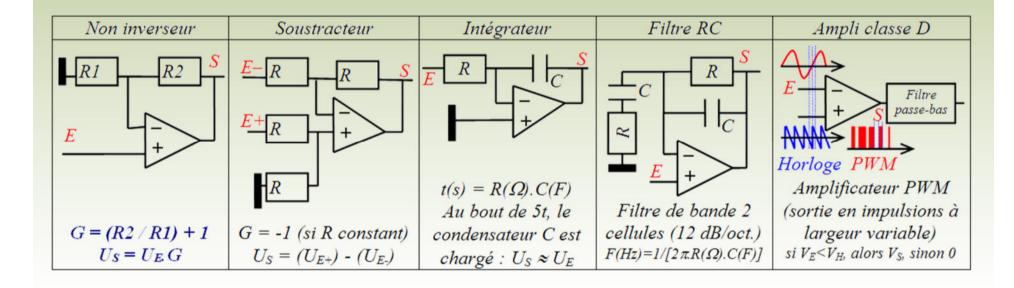

# 8-3) autres montages des amplificateurs opérationnels

• Seul le montage inverseur est au programme de l'examen de classe 2. Toutefois quelques questions portant sur le gain du montage non inverseur ont été recensées et il existe de nombreux autres montages. En voici quelques-uns ci-dessous:

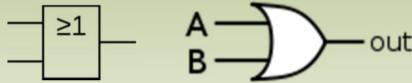

- A ce jour, une seule question recensée à l'examen car les « circuits logiques simples » sont au programme.

- les circuits logiques sont des <u>opérateurs binaires</u> : ils ne connaissent que deux positions : <u>0 ou 1</u>.

- Les <u>niveaux logiques</u> sont à 1 pour une tension proche de 5 V et à 0 pour 0 V (logique TTL).

- les portes peuvent avoir 2 ou plusieurs entrées mais une seule sortie.

| Circuit       | Circuit logique ET (AND ou &)               |   | OU (OR ou ≥1) | NON ET (Nand)                                            | OU Ex (EXOR ou =1)                                     |                                                          |  |  |

|---------------|---------------------------------------------|---|---------------|----------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------|--|--|

| Schéma        |                                             |   | A & S         | $\begin{array}{c} \mathbf{A} \\ \mathbf{B} \end{array} $ | A<br>B & O-S                                           | $\begin{array}{c} \mathbf{A} \\ \mathbf{B} \end{array} $ |  |  |

| Calcul d      | Calcul de Boole                             |   | S = A.B       | S = A + B                                                | $S = \overline{A.B} \ (= \overline{A} + \overline{B})$ | $S = A \oplus B (= \overline{A}.B + A.\overline{B})$     |  |  |

|               | Α                                           | В | Sortie        | Sortie                                                   | Sortie                                                 | Sortie                                                   |  |  |

| ge ge         | 1                                           | 1 | 1             | 1                                                        | 0                                                      | 0                                                        |  |  |

| able<br>vérit | 1                                           | 0 | 0             | 1                                                        | 1                                                      | 1                                                        |  |  |

| Ta            | Table 1 0 0 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |   | 1             | 1                                                        | 1                                                      |                                                          |  |  |

|               |                                             |   | 1             | 0                                                        |                                                        |                                                          |  |  |

F-93330 Neuilly sur Marne

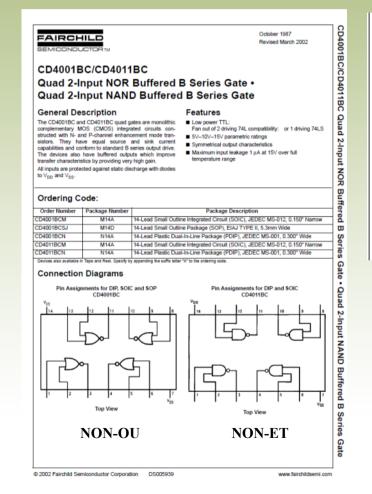

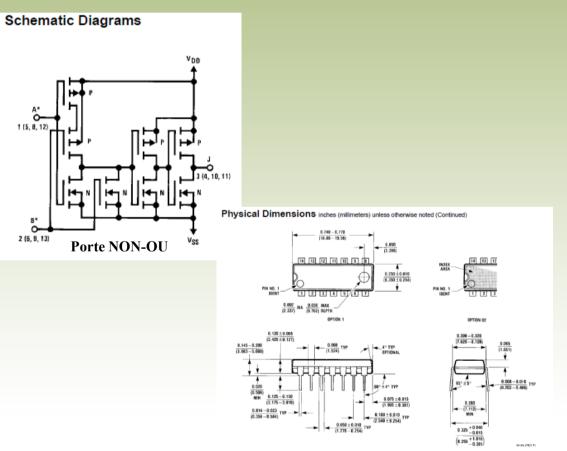

• Portes logiques 4001 NOR et 4011 NAND (4 portes à 2 entrées) extraits de la datasheet - <a href="http://f6kgl.free.fr/4001.pdf">http://f6kgl.free.fr/4001.pdf</a>)

14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Package Number N14A

Sortie

A OU B

0

George Boole 1815 - 1864 Algèbre binaire (1844)

Otto Schmitt

1913 - 1998

Brevet de la « bascule à seuil » (circuit logique) (1934)

Le <u>calcul booléen</u> est une approche algébrique de la logique

permettant de modéliser des raisonnements

- Lecture d'une table de vérité

- Exemple : porte OU (+ en calcul booléen)

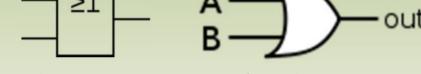

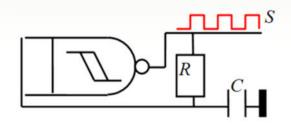

hystérésis et <u>trigger de Schmitt</u>

hystérésis (du grec υστεροζ (husteros) = après, plus tard) : propriété d'un système qui tend à demeurer dans un certain état quand la cause extérieure qui a produit le changement d'état a cessé.

- trigger = gâchette en anglais

- utilisation en oscillateur

Entrée

Α

0

0

1

1

В

Transfer characteristics of a Schmitt trigger

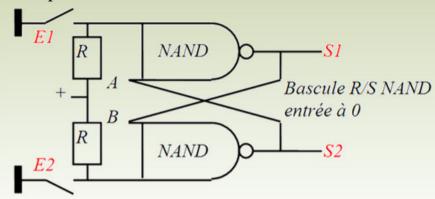

- utilisation des circuits logiques pour créer une mémoire (bascule R/S)

- R/S = Reset (=remise à Zéro) / Set (= positionner à 1)

- ces montages portent aussi le nom de « flip-flop »

- la dernière valeur présente en entrée est recopiée et conservée sur la sortie

- les sorties S1 et S2 sont complémentaires (si S1 = 0 alors S2 = 1)

### Recopie sur S la dernière entrée à 0

### Recopie sur S la dernière entrée à 1

- cette technologie pour créer des « bits de mémoire » n'est plus utilisée car

- elle nécessite de nombreux composants à créer sur la puce

- elle est très gourmande en énergie

- le circuit doit toujours être alimenté pour garder les bits en mémoire

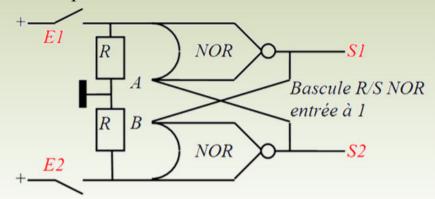

- De nos jours, les mémoires de type cartes SD sont constituées de **FET à** grille flottante

- par rapport à un FET classique, on a ajouté un simple morceau de conducteur (créant ainsi une moitié de condensateur) appelé « grille flottante » (floating gate) parce qu'elle est isolée du reste du circuit.

- la seconde partie du condensateur est le substrat P (faiblement dopé) qui sera chargé de manière inverse de la grille flottante.

- Puisque la grille flottante est isolée électriquement, son état va persister sur le long terme (<u>effet de mémoire</u>) même si le circuit n'est pas alimenté.

- selon la tension présente sur la grille, le courant

- le courant ou passera (bit = 1) si la grille est chargée positivement

- le courant ne passera pas (bit = 0) si la grille est chargée négativement

- Petit rappel de français pour commencer : l'adjectif « **digital** » est relatif aux doigts (et non pas au numérique ou aux chiffres)

- le <u>système binaire</u> repose sur les <u>bits</u> (BInary digiT, *chiffre binaire en anglais*) qui ne prennent que deux valeurs : 0 ou 1.

- un système de codage sur 8 bits formant un <u>octet</u> est utilisé en informatique.

- chaque octet est composé de 2 **demi-octets** codés en **hexadécimal** (base 16). Les valeurs 10 à 15, inconnues dans le système décimal, sont codées A à F selon la table cidessous.

| Décimal     | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    | 10               | 11               | 12   | 13   | 14   | 15   |

|-------------|------|------|------|------|------|------|------|------|------|------|------------------|------------------|------|------|------|------|

| Binaire     | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 | 1010             | 1011             | 1100 | 1101 | 1110 | 1111 |

| Hexadécimal | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    | $\boldsymbol{A}$ | $\boldsymbol{B}$ | C    | D    | E    | F    |

- Rappel: pour codifier une <u>classe d'émission</u> transmettant des données, on utilisera en troisième caractère la <u>lettre D</u>

- Transmettre des données impose de vérifier que tous les bits ont été reçus correctement. Un seul bit corrompu rend les données inexploitables.

- Pour être certain que tous les bits sont bien reçus, des systèmes de correction (CRC, contrôle de redondance cyclique) sont mis en place.

• dans une **liaison bilatérale,** après contrôle de la station réceptrice, la retransmission des données défectueuses (ARQ) par la station émettrice est demandé

lorsque **plusieurs stations reçoivent les données**, le CRC ajoutera des bits de contrôle permettant la correction automatique des erreurs (**FEC**) par les stations réceptrices.

### • Rappel de la récente modification de l'arrêté du 21/09/2000 :

Arrêté du 2 mars 2021 modifiant l'arrêté du 21 septembre 2000 modifié fixant les conditions d'obtention des certificats d'opérateur, d'attribution et de retrait des indicatifs des services d'amateur

NOR: ECOI2101792A

### Article 1

L'arrêté du 21 septembre 2000 susvisé est modifié conformément aux articles 2 à 15. [.../...]

### • Article 14

L'annexe I [programme des épreuves] du même arrêté est ainsi modifiée :

1° Au dix-septième alinéa du chapitre 4 de la première partie, les mots : « taux d'onde stationnaire » sont remplacés par les mots : « rapport d'onde stationnaire » ;

2° Le chapitre 1 er de la deuxième partie est complété par trois alinéas ainsi rédigés :

1.10. Traitement numérique du signal (DSP) [Digital Signal Process] :

- Echantillonnage et quantification;

- Démodulation des signaux ;

- Conversion analogique/digitale et digitale/analogique (ADC/DAC).

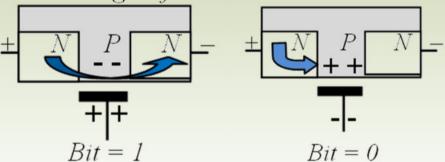

- Un <u>convertisseur analogique numérique</u> (CAN ou ADC en anglais)

- prélève un <u>échantillon</u> (e) de la tension d'un signal à intervalles fixes (fréquence d'échantillonnage,  $F_{ech}$ ).

- la tension est transformée en nombre pour chaque <u>pas de</u> <u>résolution</u> (p).

- La quantification est la résolution de l'échantillon (nombre de valeurs possibles du signal numérisé ou nombre de pas de résolution).

- La **fréquence de Shannon-Nyquist** est :

- la fréquence maximum de conversion

- égale à la moitié de la fréquence d'échantillonnage  $F_{nyquist} = F_{ech} / 2$

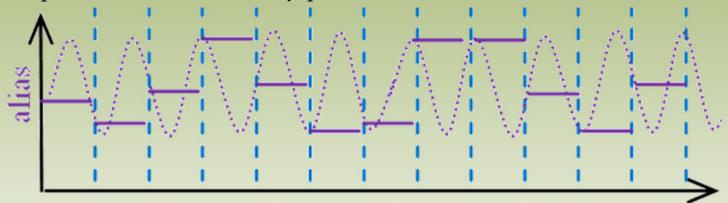

• Un <u>alias</u> est signal converti issu de fréquences supérieures à la fréquence de Shannon-Nyquist

• insérer un filtre passe-bas avant le CAN pour éliminer l'alias

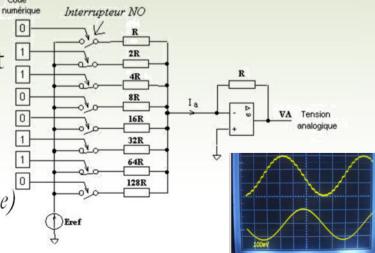

• Un <u>convertisseur numérique ana-</u> <u>logique</u> (*CNA ou DAC en anglais*) convertit un nombre binaire en tension

- ci-contre, CNA à résistances pondérées

- génère des « crénelages » qu'il faut éliminer à l'aide d'un filtre passe-bas (anti-harmonique) énergique positionné après le CNA.

- Rappel de la loi de Fourier: toutes les fonctions périodiques sont la somme de fonctions sinusoïdales de fréquences multiples de la période.

- Une <u>Transformée Normale de Fourier</u> (Discrete Fourier Transform, **DFT**) convertit un nombre fixe d'échantillons en coefficient multiplicateur des fréquences harmoniques du signal de base (<u>convolution</u>).

- Une <u>Transformée Rapide de Fourier</u> (Fast Fourier Transform **FFT**), utilisée dans les cartes-son, est un algorithme (*programme*) qui accélère le traitement en réduisant le nombre de calculs. Mais

- on perd en finesse (la définition est moins précise, risque de distorsions)

- le nombre d'échantillons à traiter doit être une puissance de 2

- Les DFT et FFT font appels aux calculs sur les **nombres complexes et les matrices** (bien au-delà de ce qui est demandé dans le programme de l'examen radioamateur, heureusement!)

- On verra dans le cours consacré aux synoptiques (§11) que:

- Les récepteurs modernes sont dotés d'un <u>étage DSP</u> situé avant l'amplificateur AF ou, de préférence, avant le démodulateur.

- Le <u>nombre de bits de codage</u> du signal détermine la dynamique du circuit (en dB, rapport entre le signal le plus puissant avant saturation et le signal le plus faible, 6 dB par bit de codage).

- Un <u>récepteur SDR</u> (Software Defined Radio) combine la conversion directe avec un traitement numérique du signal grâce à un mélangeur à double sortie (I et Q, phase et quadrature) dont le traitement numérique est beaucoup plus rapide que les FFT et qui monte beaucoup plus facilement en fréquence car le nombre d'échantillons requis pour convertir le signal est limité (mais il faut deux séries déphasés de 90 ° pour déterminer où se trouve l'extrémité du vecteur A).

- Moins gourmands en temps de calcul que les FFT et plus simples que les traitements I/Q, on trouve aussi des **filtres numériques**

- Les filtres numériques sont réalisés à partir de microcontrôleurs à l'aide de trois éléments ou opérations de base :

- le retard unitaire (pile de mémoire) -

- le gain (multiplication par un nombre donné, à adapter en fonction de la courbe du filtre à imiter),

- la sommation (addition pour superposer les signaux)

- Selon leur agencement, ces trois éléments sont suffisants pour réaliser tous les filtres numériques possibles.

- Dans un filtre, il y aura un CAN en entrée et un CNA en sortie

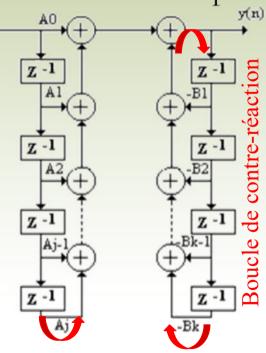

- On distingue <u>deux grandes familles</u> de filtres numériques :

- les FIR (Réponse Impulsionnelle Finie)

- imitent des filtres passifs (RC, RL ou LC)

- et les <u>IIR</u> (Réponse Impulsionnelle Infinie)

- imitent des filtres plus complexes (filtres actifs avec contre-réaction)

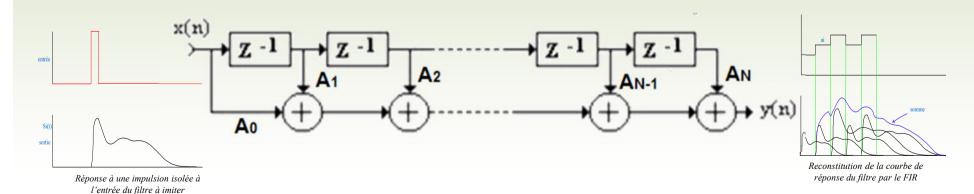

- Un <u>filtre FIR</u> (**Réponse Impulsionnelle Finie**) reconstitue la courbe de réponse en fonction du temps d'un filtre RC ou LC à partir de la réponse à une impulsion isolée en entrée de ce filtre

- les piles de mémoires (Z dans le schéma) servent de retardateurs.

- à chaque mémoire est affecté un coefficient multiplicateur (A<sub>N</sub>)

- chaque produit (valeurs dans  $Z \times coefficient A_N$ ) est additionné

- la réponse du filtre FIR est finie car l'influence de l'impulsion d'entrée s'arrête lorsque tous les retardateurs ont été activés

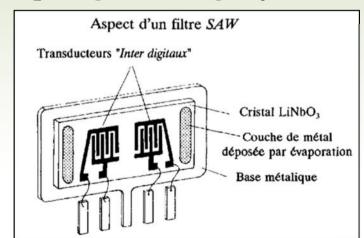

- Un <u>filtre à ondes de surface</u> (SAW, Surface Acoustic Waves) est un <u>filtre mécanique imitant un filtre</u> passe-haut ou passe-bas <u>pour une fréquence</u> <u>définie</u> par le constructeur (jusqu'à 1 GHz).

- le signal d'entrée est converti en ondes mécaniques par un <u>cristal</u> <u>piézoélectrique</u> (voir § 7.5 sur les caractéristiques du quartz).

- les ondes sont affaiblies et retardées lors de leur propagation dans le cristal avec les <u>mêmes coefficients et retards qu'un filtre FIR</u> puis sont recombinées en sortie pour générer le signal filtré.

- Mais le filtre FIR a des limites dans la reconstitution d'un filtre : un filtre actif avec contre-réaction ne peut pas être imité.

- On a alors recours au <u>filtre IIR</u> (**Réponse Impulsionnelle Infinie**), plus complexe à mettre en œuvre, dont la <u>rétroaction</u> vient corriger sur chaque retardateur le résultat du FIR à partir duquel il est construit.

- La réponse du filtre IIR est infinie car, en théorie, la rétroaction perdure indéfiniment avec le risque d'auto-osciller

- plusieurs types de montages sont possibles

- il faut adapter les coefficients multiplicateurs et le nombre de registre de mémoire en fonction du montage utilisé et du filtre à imiter

# Chapitre 8 Le montage inverseur

- Montage à partir d'un Ampli Op μA741 monté en inverseur

- A l'aide d'un voltmètre, mesurer la variation de la tension de sortie en fonction des tensions présentes sur les entrées

- En déduire la relation mathématique et le gain du circuit

Radio-Club de la Haute Île

### Le cours de F6KGL

était présenté par F6GPX

### Bon week-end à tous et à la semaine prochaine!

Retrouvez-nous tous les vendredis soir au Radio-Club de la Haute Île à Neuilly sur Marne (93) F5KFF-F6KGL, sur 144,575 MHz (FM) ou sur Internet.

Tous les renseignements sur ce cours et d'autres documents sont disponibles sur notre site Internet, onglet "Les cours" puis "Certificat Radioamateur"

f6kgl.f5kff@free.fr

https://www.f6kgl-f5kff.fr